# VOICE OF THE ENGINEER

MARCH Issue 5/2012 www.edn.com

Series resonance in power systems Pg 18

EDN.comment Pg 10

Smart wireless for your world Pg 20

Design Ideas Pg 43

Printer parking brake Pg 50

#### **ENGINEERING THE**

# NEXT GENERATION OF STEIN

Page 26

Addressing critical-area analysis and memory redundancy

Page 21

Audio-converter-subsystem design challenges in the 21st century

Page 33

# The World's Largest Selection of

electronic components available for immediate shipment!

1.800.344.4539 **DIGIKEY.COM**

2 MILLION PARTS ONLINE | 500+ INDUSTRY-LEADING SUPPLIERS | N

**NEW PRODUCTS ADDED DAILY**

Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2012 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

**TIP 1** For an inductor with the absolute maximum Q, pick one of these air core "Springs". They have flat tops for easy mounting and exceptional current ratings.

**TIP 2** If you prefer conventional chip inductors, you'll get the highest Q with our new ceramic

body 0402HP and 0603HP families. These tiny wirewound coils handle up to 2 times more current than the nearest competitor.

This new web tool finds inductors with the highest Q at your operating frequency

**TIP 3** Need to find coils with the best Q at your L and frequency? Our **Highest Q Finder** web tool tells you in just seconds. Click again to plot the L, Q, Z and ESR of up to 4 parts simultaneously.

**TIP 4** When it's time to build your prototypes, be sure to ask

us for evaluation samples. They're always free and we can get them to you overnight. To get started, visit www.coilcraft.com/Q

# Here are some high Q tips

#### **Authorized Distributor**

Texas, California, New Jersey USA

alisco MEXICO

ckinghamshire UNITED KINGDOM

Barcelona SPAIN

rive-La-Gaillarde FRANCE

indhoven THE NETHERI ANDS

Munich **GERMANY**

Assago-MI ITAL

Upplands-Väsby **SWEDEN**

Brno CZECH REPUBLIC

Raanana **ISRAEL**

Bengaluru INDI

Hong Kong, Shanghai CHINA

Bangkok THAILAND

SINGAPORE

Taipei TAIWAN

# With local support all over the world, we're fluent in technology.

Mouser delivers the components you need, on-time. And with local Technical Support and Customer Service Experts in 19 locations around the world, you'll find the newest components to launch your new design seamlessly.

**mouser.com** The Newest Products for Your Newest Designs®

# **EDN** contents

3.1.12

#### Addressing criticalarea analysis and memory redundancy

2 1 How susceptible is your design to random defects, and which areas of the layout could benefit from modifications that would provide the greatest positive effect on overall yield?

by Simon Favre, Mentor Graphics

## **Engineering the next** generation of **STEM**

Industry participants, reacting to the so-called engineering crisis, are doing what they can to foster science, technology, engineering, and math talent and encourage more students to pursue engineering careers.

by Suzanne Deffree, Managing Editor, Online

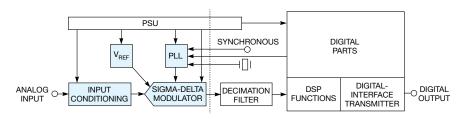

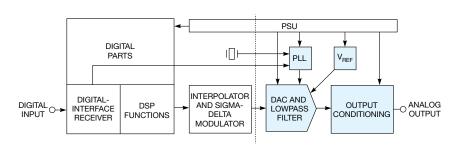

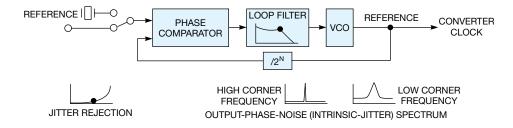

#### Audio-convertersubsystem design challenges in the 21st century

33 Some key strategies enable you to achieve optimum audio-converter performance.

by Ian Dennis, Prism Sound Group

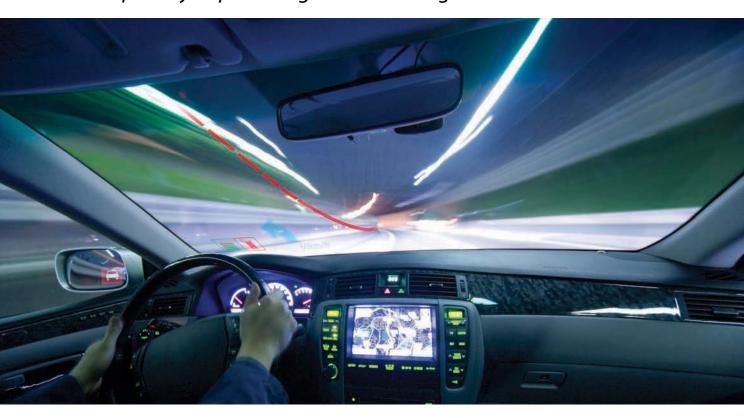

COVER IMAGE: SHUTTERSTOCK/GIULIA FINI-GULOTTA

#### DESIGNIDEAS

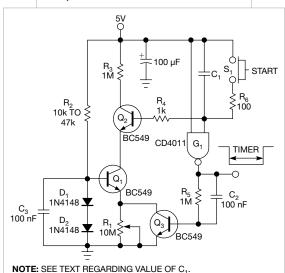

- 43 CMOS gate makes long-duration timers using RC components

- 44 Microcontroller drives piezoelectric buzzer at high voltage

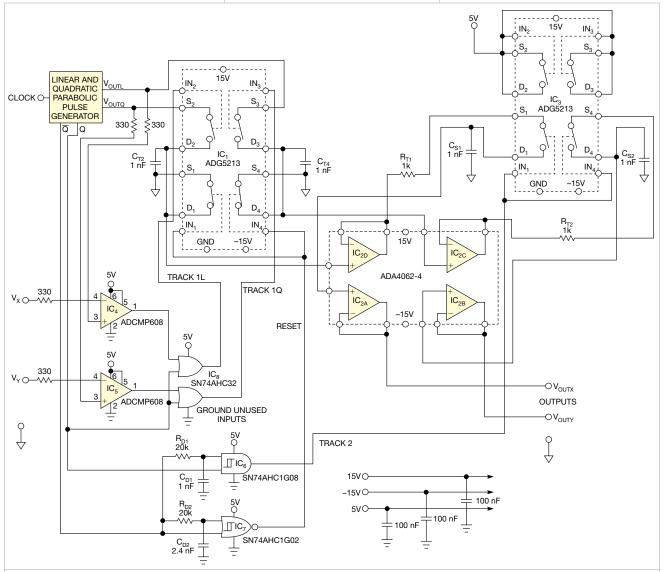

- 44 Circuit simultaneously delivers square and square root of two input voltages

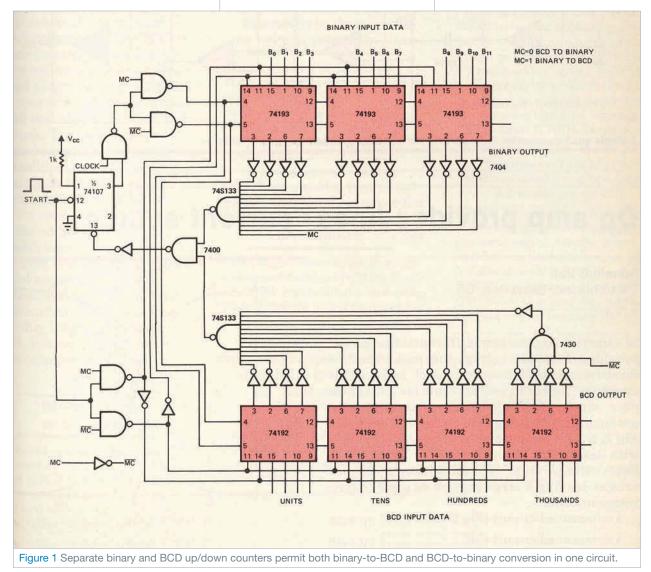

- 47 Conversion circuit handles binary or BCD

- Find out how to submit your own Design Idea: http://bit.ly/DesignIdeasGuide.

**Authorized Distributor**

# We deliver ASAP, PDQ and JIT. So, you're never SOL.

Mouser delivers the components you need, on-time. And with local Technical Support and Customer Service Experts in 19 locations around the world, you'll find the newest components to launch your new design seamlessly.

The Newest Products for Your Newest Designs®

a tti company

#### contents 3 1 12

- 12 Value-priced scopes extend bandwidth to 1 GHz

- 14 Outdoor unit brings integration to the microwave backhaul

- 14 SOC enables measurement for high-power monitoring in industrial applications

- 14 High-current storage chokes come in ERU 20 case size

- 16 3-D computer simulations reveal diffusional behavior

- 16 Digital-audio processor integrates power management

- 17 Robust three-axis sensor targets automotives

- 17 Energy-measurement IC eases utility meters' transition to smart grid

#### **DEPARTMENTS & COLUMNS**

48

- **EDN online:** Join the conversation; Content; Engineering Community

- 10 EDN.comment: Do, make, design, build, and fix the future of STEM

- 18 **Signal Integrity:** Series resonance in power systems

- 20 Connecting Wireless: Smart wireless for your world

- 48 **Product Roundup:** Test and Measurement

- 50 Tales from the Cube: Printer parking brake

EDN® (ISSN# 0012-7515) is published semimonthly by UBM Electronics, 600 Community Drive, Manhasset, NY 11030-3825. Periodicals postage paid at Manhasset, NY, and at additional mailing offices. SUBSCRIPTIONS—Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues; US, \$150 one year; \$250 two years; \$300 three years, Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 847-559-7597. E-mail: edn@omeda.com. CHANGE OF ADDRESS—Notices should be sent promptly to EDN, PO Box 3609, Northbrook, IL 60065-3257. Please provide old mailing label as well as new address. Allow two months for change. NOTICE—Every precaution is taken to ensure accuracy of content; however, the publishers cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address changes to EDN, PO Box 3609, Northbrook, IL 60065-3257. CANADA POST: Publications Mail Agreement 40612608. Return undeliverable Canadian addresses to APC, PO Box 503, RPO West BVR CRE, Rich Hill. ON L4B 4R6. Copyright 2012 by UBM. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 57, Number 5 (Printed in USA).

[www.edn.com]

Impedance Levels 10 ohms to 250k ohms, Power Levels to 3 Watts, Frequency Response ±3db 20Hz to 250Hz. All units manufactured and tested to MIL-PRF-27. QPL Units available.

#### Power & EMI Inductors

Ideal for Noise, Spike and Power Filtering Applications in Power Supplies, DC-DC Converters and Switching Regulators

Pulse Transformers

10 Nanoseconds to 100 Microseconds. ET Rating to 150 Volt Microsecond, Manufactured and tested to MIL-PRF-21038.

#### Multiplex Data Bus Pulse Transformers

Plug-In units meet the requirements of QPL-MIL-PRF 21038/27. Surface units are electrical equivalents of QPL-MIL-PRF 21038/27.

#### DC-DC Converter ransforme

Input voltages of 5V, 12V, 24V And 48V. Standard Output Voltages to 300V (Special voltages can be supplied). Can be used as self saturating or linear switching applications. All units manufactured and tested to MIL-PRF-27.

#### 400Hz/800Hz

0.4 Watts to 150 Watts. Secondary Voltages 5V to 300V. Units manufactured to MIL-PRF-27 Grade 5, Class S (Class V, 155°C available).

for FREE PICO Catalog Call toll free 800-431-1064

in NY call 914-738-1400

Fax **914-738-8225** Electronics, Inc.

143 Sparks Ave. Pelham, N.Y. 10803 E Mail: info@picoelectronics.com www.picoelectronics.com

#### Is Your 100G Testing Limited by the Speed of Your BERT?

Other BERTs

Centellax BERT (true 4x32G data rate)

#### Stay full throttle with the Centellax 100G solution.

Most BERTs serving 100G applications don't have the muscle to allow testing the channel at full speed. With maximum data rates of only 28 or 30 Gb/s, they can only handle the 4 x 28G raw data rate. This speed limitation can force you to disable encoding or FEC, not allowing the channel to operate at the full symbol rate.

The Centellax SSB32 is the only **affordable** BER tester for 100G applications with a top data rate of 32 Gb/s — enough headroom to handle virtually any level of FEC. And you won't need to pay a premium for that performance either.

Don't enter the 100G race track with just a tricycle.

# a de la contine

#### JOIN THE CONVERSATION

Comments, thoughts, and opinions shared by EDN's community

In response to "Adafruit, Sparkfun point to the democratization of hardware," a blog post by *EDN*'s Margery Conner, <a href="http://bit.ly/xs0TeF">http://bit.ly/xs0TeF</a>, Chris G comments:

"The best thing about Sparkfun and Adafruit for a casual experimenter is that they offer components and subassemblies with most of the difficult work already done. Sure, the nitty-gritty details need

to be understood before putting out a robust product, but, as my own efforts have shown, just trying to get a microprocessor to communicate to another device over I<sup>2</sup>C can be daunting enough while also working out the communication handshaking, even after reading the device maker's spec sheets. Having these things worked out in an experimenters' kit is the reason that these companies are the ones to watch."

# In response to "Cow tipping," a Tales from the Cube column by Arnold N Simonsen, http://bit.ly/zaho6V, "bandit" comments:

"A moooving story, ranging by degrees from fence post to fence post. Our intrepid engineer boresighted right to the horns of the problem. The solution? Beefing up the trailer site, making hamburger of the problem, avoiding the cow patties in his path. Another government job properly steered away from danger."

EDN invites all of its readers to constructively and creatively comment on our content. You'll find the opportunity to do so at the bottom of each article and blog post. To review current comment threads on EDN.com, visit <a href="http://bit.ly/EDN\_Talkback">http://bit.ly/EDN\_Talkback</a>.

#### 5 ENGINEERS: WHY DID YOU BECOME AN ENGINEER?

We asked, and you're answering. More than 185 comments have been posted so far, ranging from "I wanted to make the world a better place" to "The devil made me do it." Share what it was that inspired you to pursue engineering as a career path in this blog post's comment section.

#### http://bit.ly/yD1hsg

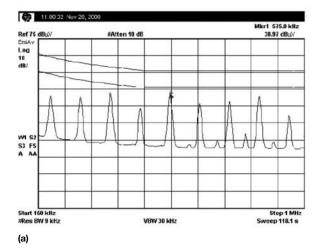

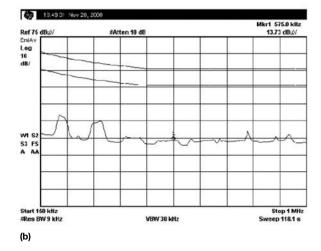

#### SAMSUNG LED-LIGHT-BULB TEARDOWN INCLUDES OBJECTIVE DIMMING NUMBERS

Samsung sent *EDN*'s Margery

Conner an LED-replacement bulb to

put through its paces and then tear

down. How does the bulb do with

the onerous TRIAC-dimming test?

Pretty darned good, and Margery

has posted a graph to prove it.

http://bit.ly/xElkmE

#### **ENGINEERING COMMUNITY**

Opportunities to get involved and show your smarts

#### FREE BEER!

Now that we have your attention, be sure to register for Design West, a new event this year that collocates seven summits for four days of training and education, hands-on knowledge exchanges, teardowns, giveaways, and more throughout the day ... and, yes, free beer, snacks, and prizes during its exponetworking event on Tuesday, March 27, 5:30 pm to 7 pm. Find out more at www.ubmdesign.com.

EDN.COMMENT

#### BY SUZANNE DEFFREE, MANAGING EDITOR, ONLINE

## Do, make, design, build, and fix the future of STEM

y now, you've seen this issue's cover. You may have even flipped through to the cover story. And you may be wondering what such a story—sans schematics, technical jargon, and just plain design basics—is doing in *EDN*. We are about engineering, after all, so where's the engineering in the cover story? In this issue's cover story, instead of presenting a design topic for you to build from, we're presenting a challenge for all of us to overcome. That challenge is how to engineer a new generation of STEM (science/technology/engineering/math) talent.

We all know the problem. Too few new engineers, as well as other STEM professionals, are graduating from US colleges. The underlying issue is that kids these days aren't taking an interest in science and math, without which they can't develop critical-thinking skills and that sense of curiosity that contributes to entrepreneurial attitudes and life-long discovery.

Many people reading this editorial will say that we shouldn't be encouraging kids to study STEM because of a claimed lack of engineering jobs in the United States. This situation isn't just about jobs, though. It's about creating a climate of more creative and more intelligently thinking, and, ultimately, more proactive people. We can be sure of this: If engineers—who are creative, intelligent, productive people—ran things in this country, we'd all be in a better position when it came to the employment market, as well as many other hot-button concerns.

Engineering the next generation is about creating leaders who can help us build a better tomorrow. Although these leaders would preferably be new engineers, we also need more professionals in other fields, inside or outside STEM, who think like

engineers to help brighten the picture.

It's easy to point fingers; politicians do it all the time. But, as engineers, you do, you make, you design, you build, and you fix. Those abilities—not the degree you received—make you an engineer. Those same principles make the topic of next-generation STEM talent an engineering issue. We know there is a problem. Let's do something to fix it; let's engineer it.

As issues about STEM evolve, you'll see more content like this cover story on how to engineer this crisis into a healthier state. This content will appear in print, on EDN.com, through our social-media efforts, in our webcasts, and through the events we attend. For example, EDN is presenting a Design West panel on this topic on March 28 at the San Jose McEnery Convention Center. Look for it in the show-floor theater at 1:30 pm. After the panel, we'll also host a networking session in which we'll invite experienced engineers and executives to connect with incoming and new STEM talent.

Further, the IEEE has asked me and my colleague at UBM Electronics, Naomi Price, online brand manager for Innovation Generation, to speak at its Integrated STEM Conference on March

If engineers—who are creative, intelligent, productive people—were running things, we'd all be in a better position in the employment market.

9, at the College of New Jersey (Ewing, NJ). Naomi and I will also attend the USA Science and Engineering Festival in Washington, DC, during the last weekend in April to celebrate the brilliance this next generation brings to the game.

We hope to see you at these events in March and April. You can find more information about them in the online version of this editorial. In the meantime, we invite you to share your own thoughts on what we can all be doing to help encourage the next generation of STEM at http://bit.ly/zC6wYA.

We'll bring back the design focus in *EDN*'s March 15 cover story. But don't walk away thinking that this need for more STEM talent isn't an engineering topic. It is vital to the future of engineering itself and something that we can together engineer—do, make, design, build, and fix—toward a better future. **EDN**

Contact me at suzanne.deffree@ubm.com.

#### SENIOR VICE PRESIDENT. **UBM ELECTRONICS**

David Blaza 1-415-947-6929; david.blaza@ubm.com

#### DIRECTOR OF CONTENT. **EDN AND DESIGNLINES**

Patrick Mannion 1-631-543-0445; patrick.mannion@ubm.com

#### **EXECUTIVE EDITOR, EDN AND DESIGNLINES**

Rich Pell Consumer 1-516-474-9568; rich.pell@ubm.com

#### MANAGING EDITOR

Amy Norcross Contributed technical articles 1-781-869-7971; amy.norcross@ubm.com

#### MANAGING EDITOR, ONLINE

Suzanne Deffree Electronic Business, Distribution 1-631-266-3433; suzanne.deffree@ubm.com

#### SENIOR TECHNICAL EDITOR

Steve Taranovich Analog, Systems Design 1-631-413-1834; steve.taranovich@ubm.com

#### **TECHNICAL EDITOR**

Margery Conner Design Ideas, Power Sources, Components, Green Engineering 1-805-461-8242: margery.conner@ubm.com

#### **DESIGN IDEAS** CONTRIBUTING EDITOR

Glen Chenier edndesignideas@ubm.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-869-7969; frances.granville@ubm.com

#### **ASSOCIATE EDITOR**

Jessica MacNeil, 1-781-869-7983; jessica.macneil@ubm.com

#### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Brian Bailey, brian\_bailey@acm.org Robert Cravotta, robert.cravotta@embeddedinsights.com

#### VICE PRESIDENT/DESIGN DIRECTOR

Gene Fedele

#### **CREATIVE DIRECTOR**

David Nicastro

#### ART DIRECTOR

Giulia Fini-Gulotta

#### **PRODUCTION**

Adeline Cannone, Production Manager Laura Alvino, Production Artist Yoshihide Hohokabe, Production Artist Diane Malone, Production Artist

#### EDN EUROPE

**Graham Prophet** Editor, Reed Publishing gprophet@reedbusiness.fr

#### EDN ASIA

Huang Hua Operations General Manager huang.hua@ednasia.com Grace Wu Associate Publisher grace.wu@ednasia.com Vivek Nanda, Executive Editor vnanda@globalsources.com

#### EDN CHINA

Huang Hua Operations General Manager huang.hua@ednchina.com Grace Wu Associate Publisher grace.wu@ednasia.com Jeff Lu, Executive Editor ieff.lu@ednching.com

#### EDN JAPAN

Masaya Ishida, Publisher mishida@mx.itmedia.co.jp Makoto Nishisaka, Editor mnishisa@mx.itmedia.co.jp

#### **UBM ELECTRONICS** MANAGEMENT TEAM

Paul Miller Chief Executive Officer UBM Electronics, UBM Canon (Publishing), UBM Channel, and UBM Design Central Kathy Astromoff. Chief Executive Officer, UBM Electronics Brent Pearson. Chief Information Officer David Blaza, Senior Vice President Karen Field,

Senior Vice President, Content Jean-Marie Enjuto, Vice President, Finance Barbara Couchois, Vice President, Partner Services and Operations

Felicia Hamerman. Vice President, Marketing Amandeep Sandhu, Director of Audience Engagement and Analytics

For a complete list of editorial contacts, see http://ubmelectronics.com/editorial-contacts

# XIMU RECEPTAC

## OVER 800 STYLES AND OPTIONS IN STOCK

Suitable for applications subject to high amounts of vibration and shock, Mill-Max pins and receptacles are available in diameters from .008" (.20mm) to .250"

(6.35mm). Receptacles feature a 4 or 6 finger beryllium copper or beryllium nickel contact to ensure integrity of connection for use in the harshest environments.

Don't see what you need? Rapid prototyping and custom designs are our specialty.

www.mill-max.com/EDN621

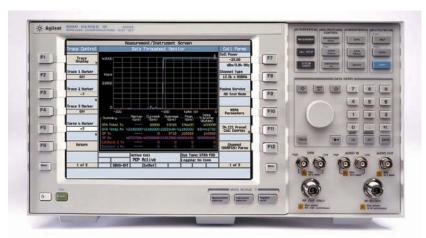

## Value-priced scopes extend bandwidth to 1 GHz

gilent is adding four models to its InfiniiVision 3000 X series of valuepriced digital oscilloscopes, doubling to 1 GHz the maximum bandwidth, increasing the maximum acquisition rate from 4G to 5G samples/sec/active channel, and adding such optional features as a ±3-digit digital voltmeter/five-digit frequency counter that uses the same signal leads as the scope. This option simplifies simultaneous numeric measurements and waveform display. The company has also expanded its Waveform Builder software line, which supports the built-in function/waveformgenerator option. Memory depth is, optionally, 4M points/channel, and the maximum waveform-update rate remains 1 million waveforms/sec, a spec that only one competitor can equal without the use of special operating modes.

The wider bandwidth and increased acquisition rate position the new units, which include two- and four-channel analog scopes and mixed-signal oscilloscopes, to invade portions of the turf of higher-priced

scopes. US list prices for 1-GHz-bandwidth units start at \$9950 for a unit with two analog channels. According to Agilent, the 3000 X series' designedin upgrade capabilities more effectively extend the

instruments' life-

time and preserve users' investment

than do competitive devices. Prices for upgrades from lower analog bandwidths to 1 GHz begin at \$2340.

The company has also announced the \$1000, 1-GHz N2795A active probe. The probe has one-quarter the input capacitance of passive probes that provide similar bandwidth. Although Agilent specs this device's bandwidth at 1 GHz, a company spokesman says that, when you use the 1-GHz probe with the 1-GHz scope, the combined -3-dB bandwidth remains higher than 1 GHz. The probe also sports a pair of LED "headlights" that make it easier to find probe points on dense PCBs. You can use one or two of these probes with a 1-GHz-bandwidth 3000 X scope. For applications that require both probing and 1-GHz bandwidth on more than two channels, the company recommends its 1157A probes, which draw less power from the scope's internal power supply.

by Dan StrassbergAgilent Technologies,

www.agilent.com.

**TALKBACK**

"I became an engineer because I like clarity and specifics. I've learned from experience that, whenever a company avoids giving specifications, especially those involving price, be wary of fraud. Too many companies substitute [disreputable] marketing strategies for engineering transparency."

—EDN reader Neil Baker, in EDN's Talkback section, at http://bit.ly/ wLqanx. Add your comments.

The four-channel MSO-X 3054A provides 1-GHz maximum bandwidth, 2M-sample/channel acquisition memory (4M samples optional), and 16 digital timing-analysis channels. A digital multimeter/frequency counter with on-screen readout, a built-in function/waveform generator, and a 1-GHz active probe are extra-cost options.

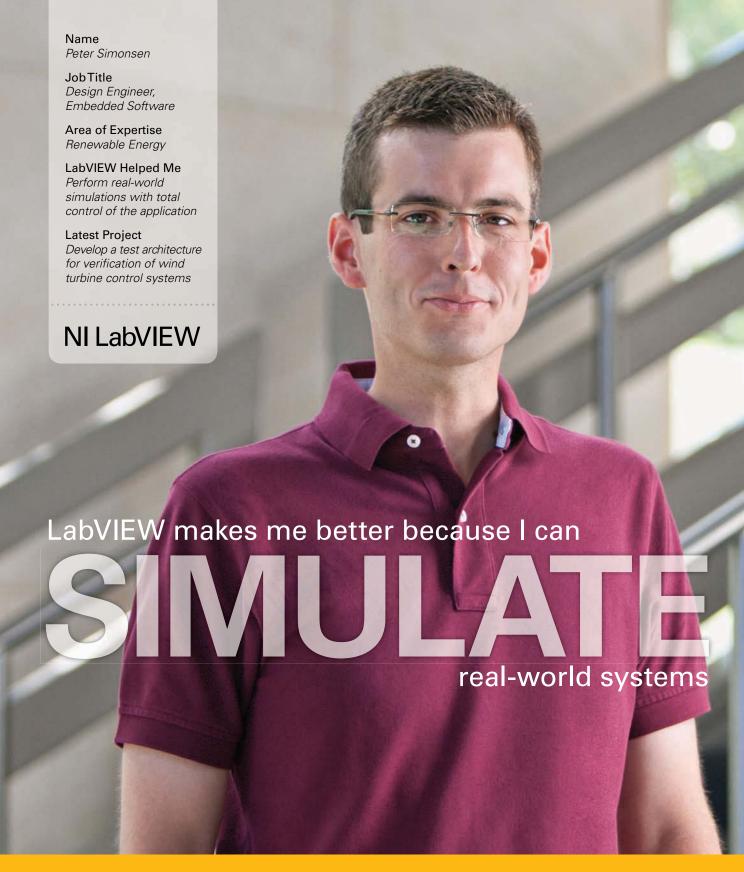

>> Find out how LabVIEW can make you better at ni.com/labview/better

800 453 6202

#### Outdoor unit brings integration to the microwave backhaul

roadcom's new BCM85810 microwave

of as many as 10 offthe-shelf application-specific standard products, including IF and RF synthesizers, low-noise amplifiers, automatic-gain controllers, bandpass-filter banks, lowpass-filter banks, IR mixers, variable-gain and variablevoltage attenuators with automatic-gain control of more than 70 dB, and power-amplifier drivers and power detectors.

The BCM85810 addresses the need for higher bandwidth and faster time to market in

microwave split-mount and full- and all-outdoor units. With support for high modulation and with only two variants to cover all standard point-to-

point microwave-frequency bands and channel outdoor-unit IC combines the functions | bandwidths, the BCM85810 simplifies system

manufacturing, deployment, and inventory management, according to the company.

The device offers an automatic-gain-control dynamic range of more than 70 dB, internal power controls, and on-chipselectable baseband filters. It maintains receiver output power over the full input-power range and complies with European Telecommunications Stan-

dards Institute and Federal Communications Commission standards. - by Fran Granville **▶Broadcom**, www.broadcom.com.

The BCM85810 fulfills the need for higher bandwidth in outdoor units.

#### SOC enables measurement for high-power monitoring in industrial applications

axim's new Teridianbased, three-phase 78M6631 powermeasurement system on chip embeds power monitoring into high-load applications. The self-contained and customizable system suits use in industrial panels and motors, solar-panel inverters, storage power supplies, and data centers. The device's embedded

metrology engine includes a range of embedded energy diagnostics, including power factor, harmonic distortion, voltage sag, and voltage dip. The 78M6631 also provides better than 0.5% system accuracy across a 2000-to-1 dynamic range, enabling the use of the lowest-value shunt for the current sensor, thus reducing heat and parasitic-power loss.

Preloaded firmware supports both Delta and Wye threephase applications, reducing both development costs and time to market. The 78M6631 SOC is available in a lead-free QFN package and sells for \$5.78 (1000).

#### -by Fran Granville ▶Maxim Integrated Products.

www.maxim-ic.com.

#### **DILBERT By Scott Adams**

#### **HIGH-CURRENT STORAGE** CHOKES COME IN **ERU 20 CASE SIZE**

TDK-EPC has extended the standard EUR 13 and **ERU 25 series of Epcos** power inductors with the new ERU 20 series. The devices have inductance values of 1 to 35 µH and a current rating of 93 to 50A. Their dc-resistance values range from 0.62 to 7 m $\Omega$ . The ERU case sizes suit use in highcurrent, low-voltage dc/ dc converters, pointof-load converters, and multiphase modules. The design employs ferrite cores and flat-wire winding technology. Low core losses and efficient design with self-supporting winding permit ultracompact dimensions and good storage density.

The inductors have a 21×21.5-mm<sup>2</sup> footprint and an insertion height of 9.8 to 14.2 mm, depending on type. The **ROHS-compatible de**vices are also available in customer-specific versions. Applications include power supplies in telecommunications and IT systems and inverters for photovoltaic systems.

-by Fran Granville TDK-EPC

ductance values of 1 to 35 μH and a current rating of 93 to 50A.

Distributed

Factorized

**Power Management**

Innovation

Integration

Performance

Speed

Efficiency

Density

## More Flexibility

Vicor gives power system architects the flexibility to choose from modular, plug-and-play components, ranging from bricks to semiconductor-centric solutions with seamless integration across all power distribution architectures. From the wall plug to the point of load.

Don't let inflexible power products slow you down.

Choose from limitless power options to speed your competitive advantage.

#### Flexibility. Density. Efficiency.

Trust your product performance to Vicor

Support

Expertise

Productivity

Reliability

Qualified

## 3-D computer simulations reveal diffusional behavior

team of researchers at the Georgia Institute of Technology is exploring how nanoparticles move and diffuse on a surface or in a fluid under nonideal to extreme conditions. Rigoberto Hernandez, a professor at the university's school of chemistry and biochemistry, investigates these relationships by studying 3-D particle-dynamics simulations on high-performance computers. His findings focus on the movements of a spherical probe among static needles (Reference 1).

Hernandez and his former doctoral student, Ashley Tucker, assembled the rodlike scatterers in one of two states during his simulations: disordered, or isotropic, and ordered, or nematic. When disordered, the nanorods point in various directions and typically diffuse normally in all directions. When every rod points in the same direction, the particle, on average, diffuses more in the same direction as the rods than against the grain of the rods. In this nematic state, the probe's movement mimics the elongated shape of the scatterers.

Surprisingly, however, the particles sometimes diffuse faster in the nematic environment than in the disordered environment. That is, the channels left open between the ordered nanorods don't just steer nanoparticles along a direction; they also enable them to speed right through. As the density of the scatterers increases, the channels become more crowded. The particle diffusing through these assemblies slows dramatically in the simulation. Nevertheless, the nematic scatterers continue to accommodate faster diffusion than do disordered scatterers, according to the researchers.

"These simulations bring us a step closer to creating a nanorod device that allows scientists to control the flow of nanoparticles," says Hernandez. "Blue-sky applications of such devices include the creation of new light patterns, information flow, and other microscopic triggers." For example, if scientists need a probe to diffuse in a specific direction at a particular speed, they could trigger the nanorods to move

into a specified direction. When they need to change the particle's direction, they could trigger scatterers to rearrange into a different direction. The trigger could even be the absence of sufficient nanoparticles in a given part of the device. The ensuing reordering of the nanorods would then drive a repopulation of nanoparticles that would then be available to perform a desired action, such as to stimulate light flow.

The National Science Foundation-funded work targets a better understanding of the motion of particles within complex arrays at the nanoscale. The work has significant long-term implications on device fabrication and performance at such scales.

## by Fran GranvilleGeorgia Institute of Technology,

www.gatech.edu.

#### REFERENCE

■ Tucker, Ashley K, and Rigoberto Hernandez, "Diffusion of a Spherical Probe through Static Nematogens: Effect of Increasing Geometric Anisotropy and Long-Range Structure," *The Journal of Physical Chemistry B*, Dec 8, 2011, pg 1328, http://bit.ly/zFH6Yd.

Georgia Tech Professor Rigoberto Hernandez and his former doctoral student, Ashley Tucker, assembled the rodlike scatterers in one of two states during simulations: disordered, or isotropic, and ordered, or nematic.

#### Digital-audio processor integrates power management

onexant's new dual-core, 32-bit CX20805 digital-audio processor integrates high-speed USB 2.0, an 800-MIPS DSP, and support for as many as eight endpoints. The chip comes with a C compiler, software tools, and a suite of DSP algorithms. It uses the vendor's CAPE (Conexant audio-processing-engine) architecture. Each dual-core DSP includes dual media-access controllers operating at 200 MHz. The CX20805 also includes 520 kbytes of embedded SRAM and 352 kbytes of embedded ROM; a full-duplex, I2S-multiplexed stereo with a four-channel

PCM interface; an I<sup>2</sup>C master and slave; and an SPI master and slave.

Other features include support for a quad digital microphone with pulse-density modulation, SPDIF receiving and transmitting, tricolor PWM-LED drivers, and 24 programmable I/Os. A custom audio bus connects to multichannel audio

devices, and the product has an AES 128 decryption engine, an on-chip logic

The CX20805 processor supports eight endpoints.

analyzer and JTAG, a UART, and dedicated peripheral and memory-to-memory DMA channels. Integrated dc/dc conversion, power gating, power retention, dynamic voltage scaling, and frequency scaling reduce power consumption.

Housed in a 9×9-in., 116-pin, dualrow QFN package, the device sells for \$5.50 (10,000). Evaluation kits are available to qualified customers and partners.

by Fran GranvilleConexant Systems Inc, www.conexant.com.

# 03.01.12

#### Robust three-axis sensor targets automotives

■ TMicroelectronics' new A3G4250D angularrate gyroscope aims to add position accuracy and stability to a range of automotive applications, including indash navigation, telematics, and vehicle-tolling systems. The AEC-Q1000-qualified gyroscopes provide accurate measurements of angularmotion detection, significantly enhancing dead-reckoning and map-matching capabilities in car-navigation and telematics applications.

By monitoring motion, distance traveled, and altitude, dead-reckoning systems compensate for the loss of satellite signals indoors and in urban canyons between tall buildings. Precise gyroscope read-

ings also improve map-matching, the process of aligning a sequence of observed user positions with the road network on a digital map, such as those for traffic-flow analysis and driving directions.

The device employs one sensing structure for motion measurement along the orthogonal yaw, roll,

and pitch axes, eliminating interference between the axes, increasing measurement precision, and providing output stability over time and temperature. The A3G4250D measures angular rates to ±250°/sec. An on-chip IC interface converts the angular motion into a 16-bit

digital bit stream that transmits to a dedicated microcontroller chip through a standard SPI or I<sup>2</sup>C protocol. The device provides interrupt and data-ready output lines and four user-selectable output-data rates.

The 3V-single-supply sensor integrates power-down

The three-axis A3G4250D automotive gyroscope provides motion measurement along all three orthogonal axes.

and sleep modes and an embedded first-in/ first-out memory block for power management. The A3G4250D embeds an 8-bit temperature sensor and

operates at an extended temperature range of –40 to +85°C. The device is robust against EMI and withstands shocks as large as 10,000g. It sells for \$6 (1000).

—by Fran Granville ▶STMicroelectronics, www.st.com.

## Energy-measurement IC eases utility meters' transition to smart grid

Look out, you spinning-disk utility meters out there. Your days of ruling the power line are coming to a at least you'll get that impression as smart meters that employ electronic sensing to provide advanced connectivity continue to replace the venerable glass-encased meters that have served the utility industry for more than 100 years. The latest entry in the metering-IC arena is the CS548x/9x family from Cirrus Logic. The family supports singleand multiple-phase ac-line measurement of voltage and current through per-channel ADCs and then calculates the power usage using an internal digital core.

Other ICs for this application use SOC front ends and separate communications processors, but the topology of the Cirrus devices puts the converters and calculating core at the front end, lowering cost through the elimination of

unneeded hardware blocks, according to the vendor, and using optocouplers, thus requiring fewer signal lines to isolate. Applications for these IC-based energy meters go beyond residential lines and their metering. Vendors are looking to incorporate them into appliances, smart power strips, power supplies, and power-hungry servers in enterprise applications.

The devices offer measurement accuracy for both active and reactive power (power factor) of 0.1% over a 4000-to-1 dynamic range, surpassing industry requirements, whereas current rms measurement accuracy is 0.1% over a 1000-to-1 range with readings using simultaneous-sampling converters and 24-bit, fourth-order delta-sigma modulators. On-chip measurements include active, reactive, and apparent power; rms voltage and current; power factor; and line frequency.

For transducer I/O-critical to this application—the ICs support shunt resistor, current transformer, and Rogowski-coil pickups, with configurable digital outputs for energy pulses, zero crossing, or energy direction. The chip's selfcalibration time is less than 2 sec, which Cirrus claims is one-tenth the time of other available devices. Calibration time is important because these meters and their sensors require calibration at the factory's production line. At the other side of the I/O situation, the family offers SPI and UART interfaces, depending on IC model. The devices operate from a single 3.3V supply, and power consumption is less than 13 mW.

The CS548x/9x family includes two-, three-, and four-channel front ends, which are available in 16-lead SOIC, 24-lead QFN, and 28-lead QFN packages. Prices begin at 75 cents (100,000) for the smallest member of the family.

-by Bill Schweber

Cirrus Logic, www.cirrus.com.

#### BY HOWARD JOHNSON, PhD

# Series resonance in power systems

M

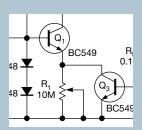

any digital systems suffer excessive power-supply noise at frequencies relating to the system clock. Could a series-resonant circuit, such as the one in **Figure 1**, connected between the power and the ground planes attenuate that noise? The answer can be yes, but only if your circuit satisfies the following improbable conditions.

First, the frequency of the system clock must remain fixed. In systems without a crystal-controlled clock, the clock frequency may wander ±30% or more. Low-power systems often slow the clock to conserve power when idle. High-performance systems sometimes come in speed variants, for which customers pay extra to gain performance. As a diagnostic test, a designer may slow the system clock to reveal certain timing-related failures. No power-supply-noise-mitigation strategy employing careful tuning of exact noise fre-

$F_{RES} = \frac{1}{2\pi\sqrt{LC}}$  R C

Figure 1 The impedance of this network attains its smallest value at the resonant frequency.

quencies can possibly work under these conditions.

The allure of a series-resonant circuit is that it permits the use of a smaller value of capacitor than otherwise might be necessary if you match that capacitor with appropriate values of inductance and resistance, creating the series-resonant effect. Unfortunately, the smaller the capacitor, the more precise the circuit must become.

For example, a capacitor of one-fifth the ordinary value requires capacitor and inductor components with ±10% tolerance. A capacitor of one-tenth the normal value requires ±5% tolerance, and so on. It is difficult to implement high-frequency inductors with such tight tolerances. If you think of the layout inductance as fixed and plan a smaller value of capacitance to place the series-resonant point at a favorable location, you will face the same difficulty: You cannot easily control the exact values of capacitance and inductance.

The clock must play continuously, repeating forever without stops or gaps. If the clock stops, your resonant circuit will spin on, plunging out of control, creating disturbances just as bad as the problem you were trying to mitigate. When the clock restarts, the resonant circuit takes many cycles to catch up—providing zero benefit during that period. A resonant

circuit is useful only with continuous stimulation. It is powerless to prevent noise from random data events.

You must place the series-resonant circuit within a small fraction of one wavelength of any device that it is protecting. Within that limited radius, the spreading inductance of the power and ground planes modifies the effective series inductance of the resonant circuit. Consequently, the exact positioning of a resonant circuit matters tremendously, so you cannot alter the layout without implementing a complete redesign. Even worse, a resonant element that provides substantial attenuation for clock noise emanating from one location may provide no benefit or may even exacerbate the noise from another source.

#### In a sinusoid-based system, such as an AM or an FM radio, resonating powersupply components can provide astonishing benefits.

Last, remember that a resonant circuit attenuates noise at only one frequency. It provides little or no benefit at other harmonics of the clock rate. In a sinusoid-based system, such as an FM or an AM radio, resonating power-supply components can provide truly astonishing benefits.

In a digital system that starts and stops at various clock speeds and in which the layout constantly changes from one version to the next, the use of resonating power-supply-filter elements does not pass the KISS (keep it simple, stupid) test. A digital-power system is better served by lots of large, simple, nonresonant bypass capacitors.

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com, or e-mail him at howie03@sigcon.com.

## Look What's Happening at IMS2012!

http://ims2012.mtt.org/

Plenary Session Speaker: Steve Mollenkopf President and Chief Operating Officer, Qualcomm 3G/4G Chipsets and the Mobile Data Explosion Monday, 18 June 2012 1730-1900

The rapid growth of wireless data and complexity of 3G and 4G chipsets drives new design and deployment challenges for radio and device manufacturers along with carriers. This talk will provide a perspective on the problem from the point of view of a large, worldwide manufacturer of semiconductors and technology for cellular and connected consumer electronics devices. The increase in device and network complexity will result in significant business opportunities for the industry.

Closing Ceremony Speaker: Thomas H. Lee

Professor, Stanford University

The Fourth Age of Wireless and the Internet of Everything

Thursday, 21 June 2012 1700-1830

"Making predictions is hard, particularly about the future." The patterns of history are rarely discernible until they're obvious and perhaps irrelevant. Wireless may be an exception, at least in broad outline, for the evolution of wireless has been following a clear pattern that tempts us to extrapolate. Marconi's station-to-station spark telegraphy gave way to a second age dominated by station-to-people broadcasting, and then to today's ubiquitous people-to-people cellular communications. Each new age was marked by vast increases in

value as it enlarged the circle of interlocutors. Now, these three ages have covered all combinations of "stations" and "people," so any Fourth Age will have to invite "things" into the mix to provide another stepwise jump in the number of interlocutors. This talk will describe how the inclusion of multiple billions of objects, coupled with a seemingly insatiable demand for ever-higher data rates, will stress an infrastructure built for the Third Age. Overcoming the challenges of the coming Fourth Age of Wireless to create the Internet of Everything represents a huge opportunity for RF engineers. History is not done.

#### The IMS2012 Housing Bureau and Registration are now open!

Don't miss your chance to see the latest RF/Microwave technology advancements while accessing over 500 companies technologies and services.

Visit http://ims2012.mtt.org for complete details and to download your Program Book. Review technical sessions, workshop descriptions and exhibiting companies so you can make the most of your time at Microwave Week!

CONNECTING WIRELESS

#### BY PALLAB CHATTERJEE

#### Smart wireless for your world

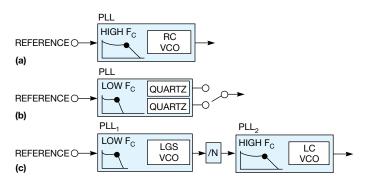

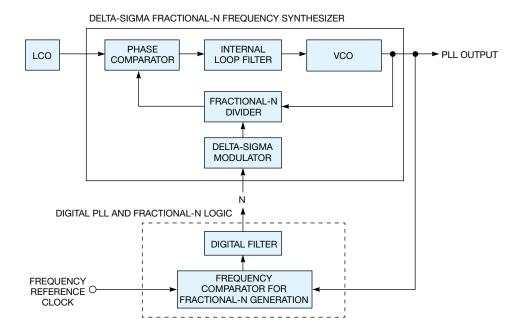

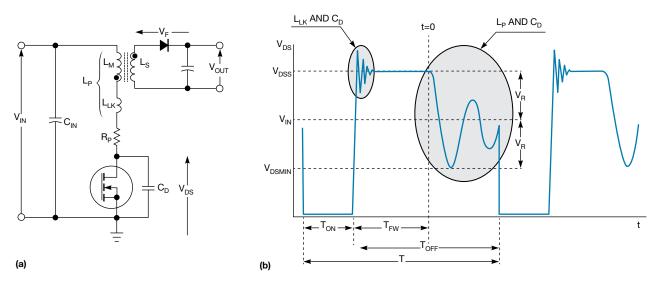

ireless for data transmission has been around for a long time and has slowly been creeping into computing devices in networks. Although RF interfaces were previously on IT and industrial-control systems, which had full-time management, the prevalence of high-performance embedded computing has created a need for distributed networks without full-time administration. This need exists independently of the platform you use—whether a microcontroller, a DSP, or a processor.

The digital-function and control side of the network has advanced to the point that it can address the self-handshaking and protocol negotiation necessary for these devices to both connect and identify themselves with minimal user intervention. A key portion of this task is the ability for the software and controller to manage the nonsequential turn-on and turn-off cycles of devices in the network as people move the devices to multiple locations and run multiple tasks without administration.

This control function is now influencing the RF side to move from individual power amplifiers, SAW (surface-acoustic-wave) filters, multiplexers, and low-noise amplifiers to full modules ranging from single-frequency transceivers to multiple-frequency cellular blocks. The resulting challenges in the RF area are spectrum crowding and the existence of multiple standards.

The RF spectra neatly divide into discrete data bands that all serve different system goals. These discrete functions, however, are all blending into the Internet of Things, which is growing daily (Figure 1). Most embedded computing devices are now transferring data to other

applications and across spectra. This trend shifts the interoperability issue to the RF from the digital as reconstructed data becomes reconstructed data in the digital domain.

The common domains for the device networks are Z-Wave in the 900-MHz spectrum; Zigbee in the 2.4-GHz spectrum, which the IEEE 802.15.4 standard covers; Bluetooth, also in the 2.4-GHz band; WiMax, which the IEEE

INTERNET OF THINGS

CONNECTED DEVICES AND NETWORKS

Figure 1 The RF spectra neatly divide into discrete data bands that all serve different system goals. These discrete functions, however, are all blending into the Internet of Things, which is growing daily.

802.16 standard covers and which supports PHY-layer devices from the 2- to 11-GHz and the 10- to 66-GHz spectra; and the mainstream wireless-data networks of Wi-Fi, under the IEEE 802.11 standards, which use multiple simultaneous data streams on the 2.4- and 5-GHz bands.

Manufacturers are integrating these device domains into peer-to-peer networks, mesh networks, LANs, and WANs. These networks supplement the multiple bands and protocols for cellular communication. Cell networks currently employ the 850-, 900-, 1800-, and 1900-MHz bands. All of these networks have made the digital shift to requiring little user intervention for communication, including automated handshaking, network connection, and device identification. The challenge for the end device is to determine which network to use. RF must appear in the end devices as a selection of one of multiple blocks.

A typical tablet PC with cellular connection may have more than seven RF-amplifier-transceiver blocks—four quad bands for the 3G cellular system, at least two blocks for 2.4 and 5G Wi-Fi bands, and one block for Zigbee or

Z-Wave home- and industrialautomation network control and interface. The Wi-Fi blocks may support as many as four antennas, which the 801.11ac spec allows, and the RF must run in parallel.

The size, power, and module integration of the required bias, amps, filters, multiplexers, and multiple signal paths are driving the analog and RF community to move to its equivalent of an RF SOC. Manufacturers are releasing these devices with full signal conditioning, and they will soon include data-conversion and postsignal-recovery capabilities that are driving both the growth and the consolidation of the industry. EDN

Pallab Chatterjee has been an independent design consultant since

# ADDRESSING CRITICAL-AREA ANALYSIS OMEMORY CANDON REDUNDANCY

HOW SUSCEPTIBLE IS YOUR DESIGN TO RANDOM DEFECTS, AND WHICH AREAS OF THE LAYOUT COULD BENEFIT FROM MODIFICATIONS THAT WOULD PROVIDE THE GREATEST POSITIVE EFFECT ON OVERALL YIELD?

BY SIMON FAVRE • MENTOR GRAPHICS

esign teams—whether using fabless, fablite, or IDM (integrated-device-manufacturer) processes—should handle the goal of reducing a design's sensitivity to manufacturing issues. The further downstream a design goes, the less likely it is that you can address a manufacturing problem without costly redesign. By promptly addressing DFM (design-for-manufacturing) problems when the design is still in progress, you can avoid manufacturing-ramp-up issues.

One aspect of DFM is determining how sensitive a physical design, or layout, is to random particle defects. The probability of a random particle defect is a function of the spacing of layout features, so tighter spacing increases random defects. Because memories are relatively dense structures, they are inherently more sensitive to random defects, so embedded memories in an SOC design can affect the overall yield of the device.

Understanding how to employ critical-area analysis becomes more important at each successive node. Memories keep getting bigger, and smaller dimensions introduce new defect types. The trade-offs that have worked well on previous nodes may give suboptimal results at the 28-nm node. For example, although manufacturers have avoided the use of row redundancy because they considered it too costly in access time, the technique becomes necessary at the 28-nm node so that vendors can achieve acceptable yields. All of these factors make careful analysis more valuable as a design tool.

#### **CRITICAL-AREA ANALYSIS**

Critical area is the area of a layout in which a particle of a given size will cause a functional failure. Critical area depends only on the layout and the range of particle sizes you are simulating. Critical-area analysis calculates val-

#### AT A GLANCE

- The probability of a random particle defect is a function of the spacing of layout features. Because memories are relatively dense structures, they are inherently more sensitive to random defects, so they can affect the overall yield of the device.

- For a critical-area-analysis tool to accurately analyze memory redundancy, it must know the repair resources available in each memory block, a breakdown of the failure modes by layer and defect type, and which repair resource these modes are associated with.

- If you do not apply redundancy, then you may need to use alternative methods to improve die yield. These methods may include making the design smaller or reducing defect rates. If you apply redundancy in designs in which it has no benefit, then you waste die area and test time, increasing manufacturing cost.

ues for the expected average number of faults and yield based on the dimensions and spacing of layout features and the particle size and density distribution that the fab measures. In addition to classic short- and open-circuit calculations, current practice in critical-area analysis includes via and contact fail-

ures. Analysis often shows that via and contact failures are the dominant failure mechanisms. You can incorporate other failure mechanisms into the analysis, depending on the defect data the fab provides.

Critical area increases with increasing defect, or particle, size. At the limit, the entire area of the chip is critical for a large-enough defect size. In practice, however, most fabs limit the range of defect sizes that they can simulate, based on the range of defect sizes that they can detect and measure with test chips or metrology equipment.

#### **DEFECT DENSITIES**

Semiconductor fabs have various methods for collecting defect-density data. For use with critical-area analysis, the fab must convert the defect-density data into a form compatible with the analysis tool. The most common format is the following simple power equation:  $D(X)=K/X^{\mathbb{Q}}$ , where K is a constant you derive from the density data, X is the defect size, and Q is the fall power. The fabs curve-fit the open and short circuits' defect data for each layer to an equation of this form to support critical-area analysis. In principle, a defect density must be available for every layer and defect type to which you will apply critical-area analysis. In practice, however, layers that have the same process steps, layer thickness, and design rules typically use the same defect-density

Manufacturers may also provide defect-density data in a table form that lists each defect's size and density value. A simplifying assumption is that, beyond the range of defect sizes for which the fab has data, the defect density is zero.

#### **CALCULATING ANF, YIELD**

To determine the average number of faults for a design, manufacturers use a tool that supports critical-area analysis, such as Mentor Graphics' Calibre, to extract the critical area for each layer over the range of defect sizes. To achieve this goal, manufacturers measure the layout and determine all of the areas in which a particle of a given size could result in a failure. The tool then uses numerical integration, along with the defect's size and density data, to calculate the

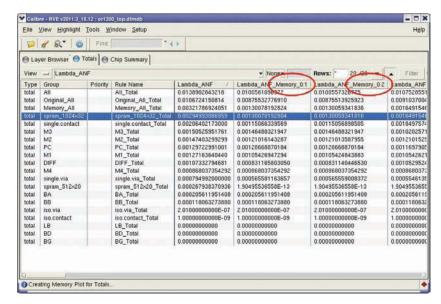

Figure 1 A critical-area analysis using Calibre shows the effects of memory redundancy on the average number of faults for different configurations.

expected average number of faults, according to the following equation:

$$ANF = \int_{D_{MIN}}^{D_{MAX}} CA(X) \times D(X)DX,$$

where ANF is the average number of faults;  $D_{MIN}$  and  $D_{MAX}$  are the minimum and the maximum defect sizes, respectively, according to the defect data available for that layer; and CA(X) and D(X) are the critical area and the defect-density data, respectively.

Once the manufacturer has calculated the average number of faults, it is usually desirable to apply one or more yield models to make a prediction of the defect-limited yield of a design. The defect-limited yield cannot account for parametric-yield issues, so be careful when attempting to correlate this figure to actual die yields. One of the simplest and most common yield models is the Poisson model: Y=E<sup>-ANF</sup>, where Y is the yield, E is a constant, and ANF is the average number of faults. It is generally simpler to calculate the average number of faults and the yield for cut layers, such as contacts and

vias, than for other layers. Most foundries define a probabilistic failure rate for all single vias in the design and assume that via arrays do not fail. This simplifying assumption ignores the fact that a large enough particle can cause multiple failures, but it greatly simplifies the calculation of the average number of faults and reduces the amount of data the fab must provide. The designer needs only a sum of all the single cuts on a layer and can calculate the average number of faults as the product of the count and the failure rate.

#### **MEMORY REDUNDANCY**

Embedded memories can account for significantly large yield loss in SOCs due to random defects. Although SOCs can use other types of memories, assume that the design uses embedded SRAM. Typically, SRAM-IP (intellectual-property) providers make redundancy an option that designers can choose. The most common form of redundancy is the use of redundant rows and columns. Redundant columns are typically easier to apply because they address only the

multiplexing of bit lines and I/O ports—not the address decoding.

To analyze failures with critical-area analysis, it is important to define which layers and defect types are associated with which memory-failure modes. By examining the layout of a typical sixor eight-transistor SRAM bit cell, you can make some simple associations. For example, by looking at the connections of the word lines and the bit lines to the bit cell, you can associate diffusion and contact to diffusion on column lines with column failures. Because contacts to diffusion and contacts to poly both connect to Metal 1, row and column layers must share the Metal 1 layer. Most of the layers in the memory design find use in multiple places, so not all defects on these layers will cause failures that are associated with repair resources. Irreparable, or fatal, defects, such as short circuits between power and ground, also occur.

#### **REPAIR RESOURCES**

Embedded-SRAM designs typically use either built-in self-repair or fuse

structures that allow multiplexing out the failed structures and replacing them with the redundant structures. Regardless of the method of applying the repair, the use of redundant structures in the design adds area, which directly increases the cost of manufacturing the design. Additional test time also increases cost, and designers may have a poor basis for calculating that cost. The goal of analyzing memory redundancy with critical-area analysis is to maximize defect-limited yield and minimize the effect on die area and test time.

A critical-area-analysis tool can accurately analyze memory redundancy only if it knows the repair resources available in each memory block, the breakdown of the failure modes by layer and defect type, and which repair resource these failure modes are associated with. Calibre can specify these variables as a series of critical-area-analysis rules. Each memory block also requires a count of total and redundant rows and columns. To identify the areas of the memory that can be repaired, you can either specify the bit-cell name that each memory block uses or use a marker layer in the layout database to allow the tool to identify the core areas of the memory.

Listing 1 provides the sramConfig memory-redundancy specification. The first two lines list the critical-area-analysis rules—that is, the type of defects that can occur—that have redundant resources for a family of memory blocks. The first two lines also contain the column rules and the row rules. These rules depend on the type and the structure of the memory block but are independent of the number of rows and columns and the redundancy resources. The last two lines describe an SRAM block design and specify, in order, the block name, the rule-configuration name, the total columns, the redundant columns, the total rows, the redundant rows, the dummy columns, the dummy rows, and the name of the bit cell. In this example, both block specifications refer to the same rule configuration, sramConfig. Given these parameters, Calibre calculates the unrepaired yield using the defect-density data that the fab provides.

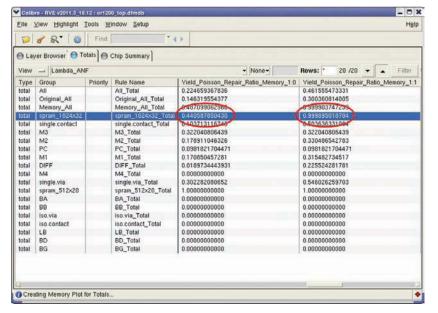

Figure 2 A critical-area analysis shows the memory-repair ratio for many parameters.

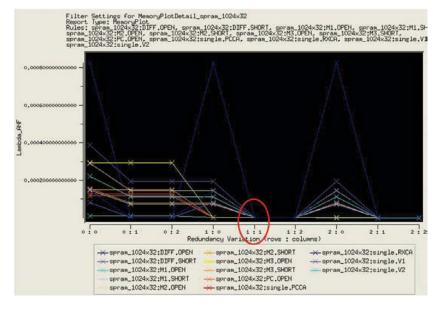

Figure 3 A memory plot shows the average number of faults for various memoryredundancy configurations. The combination of one redundant row and one redundant column causes a large decrease in the average number of faults.

#### **YIELD WITH REDUNDANCY**

Once the critical-area-analysis tool has performed the initial analysis, providing the average number of faults without redundancy, you can calculate the yield with redundancy. Calibre uses a calculation method employing the principle of the Bernoulli Trials, according to the following equation:

$$Y_R = \sum_{K=0}^{K=N_R} C(N_F, (N_F - K)) \times P^{(N_F - K)} \times Q^K,$$

where  $N_F$  is the number of functional, nonredundant memory units;  $N_R$  is the number of redundant memory units; P is the probability of success, or yield, you derive from the average number of faults; Q is the probability of a failure (1–P); and  $C(N_F, (N_F-K))$  is the binomial coefficient, which is a standard mathematical function. If the critical-

area-analysis tool can postprocess the calculations with different memory-redundancy specifications, it can present numeric and graphical output that makes it easy to visually determine the optimal amount of redundancy. The goal is to ensure the required number of good units out of a total number of units.

To see how effective memory redundancy can be, consider a hypothetical example. The memory of interest is a 4-Mbit, 32-kbit×128-bit SRAM. The goal is to realize at least 128 good units from a total of 130 units. In this case, there are two units needing repair and no defective units. Analysis determines that the unit yield considering one defect type is 0.999. The unrepaired yield of the entire core is then 0.999 raised to the 128th power, or 0.8798. If you perform the analysis for all defect types, the expected yield is approximately 0.35.

If you add redundancy to repair any unit defects, the repaired overall yield is 0.999. Memory designers use the repairratio metric to express the efficacy of memory redundancy. It stipulates that the repaired yield minus the unrepaired yield divided by one minus the unrepaired yield equals the repair ratio. A value in the high 90s is good. In this case, the repair ratio is (0.99–0.35)/(1–0.35), or 0.985.

single.VIA1 { M2 } }

sramConfig =

Using Calibre to determine an optimum redundancy configuration, you must first set up a configuration file for the tool (**Listing 2**). The bit-cell name, ram6t, tells the tool the name of the hierarchical-layout element that describes a memory unit that can be repaired and that you should consider in this analysis. This name enables the tool to calculate the critical area of the entire memory core, including all instantiations of ram6t.

With this configuration information, Calibre calculates the average number of faults for memory with no redundancy, as well as for various redundancy configurations. Figure 1 shows the results as a table with values of the average number of faults for different redundancy configurations. The table rows show the results for the entire design, for just the memory, and for specific types of defects. In the highlighted row, the average number of faults for the 1024×32-bit memory core improves substantially; the failure rate in Column 6 is half that in Column 5. To achieve this improvement, Column 6 includes one redundant row, but adding a second redundant row shows almost no further improvement (Column 7).

Figure 2 lists the effects of redundancy schemes in terms of repair ratio

by design total, by total of all analysis layers, by memory, by block, and by layers or groups. Figure 3 shows a toolcreated plot depicting the average number of faults for each redundancy configuration and for each type of defect. The combination of one redundant row and one redundant column causes a large decrease in the average number of faults, and adding resources has little further effect. From these results, you can deduce that the expected average number of faults is based on the layout of the memory under consideration and the defect density of the fab and the process. The designer can now determine the effect of various redundancy configurations on the expected yield of an embedded memory.

Memory redundancy is intended to reduce manufacturing cost by improving die yield. If no redundancy is applied, alternative methods to improve die yield may include making the design smaller or reducing defect rates. If you apply redundancy to parts of the design in which it has no benefit, then you waste die area and test time, increasing manufacturing cost. Between these two extremes, you apply redundancy or not, depending on broad guidelines. Designs with high defect rates may require more redundancy; those with low defect rates may require no redundancy. The analysis of memory redundancy using criticalarea analysis and accurate foundry-defect statistics is necessary for quantifying the yield improvement and determining the optimal configuration.EDN

#### **ACKNOWLEDGMENT**

A version of this article originally appeared on EDN's sister site, EDA Designline, http://bit.ly/ygj3Fq.

#### **LISTING 2 CONFIGURATION ENTRIES FOR 4-MBIT SRAM**

{PO.OPEN} {single.POCO} {M1 {0.4}}

{single.VIA1} {M2} {single.VIA2} {M3} }

R128x32 sramConfig 34 2 128 0 0 0 ram6t

R2048x32 sramConfig 34 2 2048 0 0 0 ram6t

LISTING 1 MEMORY-REDUNDANCY-SPECIFICATION EXAMPLE

{DIFF.OPEN} {DIFF.SHORT} {single.ODCO} {M1 {0.4}}

```

sramConfig =

{ {DIFF.OPEN} {DIFF.SHORT} {single.ODCO} {M1.SHORT}

{M1.OPEN} {single.VIA1} {M2.SHORT 0.6}

{M2.OPEN 0.6} }

{ {PO.SHORT} {PO.OPEN} {single.POCO} {M1.SHORT}

{M1.OPEN} {single.VIA1} {M2.SHORT 0.4}

{M2.OPEN 0.4} {single.VIA2} {M3.SHORT}

{M3.OPEN} }

spram_2048x32_core sramConfig 34 2 2050 2 0 0 ram6t

spram_128x32_core sramConfig 34 2 130 2 0 0 ram6t

```

#### AUTHOR'S BIOGRAPHY

Simon Favre is a technicalmarketing engineer in the Mentor Graphics Calibre division, where he supports and directs improvements to the Calibre Yield Analyzer

product. Before joining Mentor Graphics, Favre worked for Ponte Solutions, which Mentor acquired in 2008. He previously worked at other EDA companies, as well as at several semiconductor companies. Favre has bachelor's and master's degrees in electrical engineering and computer science from the University of California—Berkeley.

#

INDUSTRY PARTICIPANTS, REACTING TO THE SO-CALLED ENGINEERING CRISIS, ARE DOING WHAT THEY CAN TO FOSTER SCIENCE, TECHNOLOGY, ENGINEERING, AND MATH TALENT AND ENCOURAGE MORE STUDENTS TO PURSUE ENGINEERING CAREERS.

BY SUZANNE DEFFREE • MANAGING EDITOR, ONLINE

he engineering industry is concerned about the lack of interest in STEM (science/technology/engineering/math) studies and careers from the youth of the United States. Some in the electronics industry refer to this concern as the "engineering crisis." The fear is that, as baby boomers exit the work force, there will be too few engineers to replace them. The problem has reached all levels of public acknowledgment—from President Obama's commenting on the need for STEM graduates in his January 24 State of the Union address to Sesame Street, which is incorporating more science and technology into its programming and which made "engineer" a word of the day in a September 2011 episode.

Despite these concerns, more undergraduate students graduated in 2011 than in 2010 with engineering degrees in all of the eight top engineering disciplines—aerospace, biomedical, chemical, civil, computer, electrical and electronic, mechanical, and nuclear (Reference 1). Yet, at a year-over-year increase of only 5071 new US bachelor's degrees in engineering for a total of 84,599 new degrees in 2011, the numbers are low, especially when you compare them with estimates from the President's Council of Advisors in Science and Technology describing a need for 1 million more STEM graduates over the next decade (Reference 2). Moreover, new degrees for electrical and electronic engineering declined from 2005's high of 14,742 through 2010's 11,968, only to inch up last year with an additional 37 degrees for 12,005 new degrees total in 2011.

Steve Lyle, director of education, work-force development, and diversity at Texas Instruments, admits that the number of engineering graduates is a concern. "The competition today for STEM talent is very, very tight in the United States," he says, noting that, although the unemployment rate remains generally high in the United States, the rate is below 4% for electrical engineers. "From an education standpoint, we [and our competitors] recognize that other countries—namely, India and China—are outpacing us in the number of engineers that are coming out of their universities."

TI, like many other electronics companies, isn't ignoring the problem. Instead, it's working toward a fix. The company has invested more than \$150 million in STEM programs in the last five years and, like many others in the space, focuses its STEM efforts on student-achievement and teacher-effectiveness programs.

Like TI, Microchip Technology has engaged in STEM efforts through similar programs. "In the US political circuit, we often talk about the end product, which is jobs, but that [product] is the output of the rest of it," says Steve Sanghi, Microchip's president and chief executive officer. "We have to work on it well ahead of time and get kids excited about science, math, engineering, and technology. Corporations need to help nurture the resources and the community in which they operate. That [goal is] what we are trying to [achieve]: Prepare our future engineers; prepare our future employees; and educate the youth in math, science, engineering, and technologies."

Both Microchip and TI are proponents of FIRST (For Inspiration and Recognition of Science and Technology), an international program for children that combines hands-on, interactive robotics with a sportslike atmosphere and that provides more than \$14 million in college scholarships. FIRST started in 1989 with approximately 20 teams. It has grown to more than 26,800 teams and currently reaches nearly 300,000 students. That growth is clear evidence that STEM can attract new young talent.

Microchip is the organizing sponsor of the FIRST Robotics Competition Arizona Regional, and Sanghi, who is

#### AT A GLANCE

- Competition for STEM (science/ technology/engineering/math) talent remains high.

- The industry is using several tactics, including robotics competitions, to spark students' interest in STEM.

- Mutual respect between mentors and mentees can lead to a rewarding experience for both parties.

- "Do engineering"—allowing nextgeneration talent the experiences of actual engineering, as opposed to theory-focused education—is a strong way to encourage interest in STEM.

also a member of the FIRST board of directors, notes that the competition had to turn away teams because of venue size. Next year, organizers may add a second competition or utilize a larger venue to accommodate more teams.

Carol Popovich, senior community relations representative for FIRST and Vex Robotics and a 16-year Microchip veteran whose full-time job is to work within the community on STEM, expects further expansion in the future. She notes a dramatic 30% growth in 9- to 14-year-old participants in the local FIRST Lego League in 2011 and anticipates that these young participants will continue to explore robotics as they enter high school. Popovich is one of approximately 40 Microchip employees involved in the competition. She describes the programs as having "a high fun quotient" that keeps not just the kids but also the sponsors and mentors returning each year.

#### **MENTORING AND HIRING**

Daniel Kinzer, a technical-support engineer who has worked at Raytheon for 28 years, started volunteering six years ago with his local high school's robotics club. The club's 40 students are spread over three FIRST Tech Challenge teams, which Raytheon sponsors. On a strictly volunteer basis, he spends four to five hours a week at Palm Harbor University High School (Palm Harbor, FL) during the building cycle and double that time, plus weekends, during competitions. "If I could retire, I'd do this full time," Kinzer says. "I'm not sure who's

having more fun—me or the kids!"

Kinzer requires his teams to apply a full discipline to their projects. "The robotics portion isn't just robotics. It's mechanics, it's physics, it's programming, [and] it's engineering documentation," he says. "It's the difference between a bunch of kids molding things together until it works and [kids] really thinking out the process and identifying how things are going to work. Those are the types of abilities that [make you not only al successful engineer but also successful in life." As a mentor, Kinzer recognizes that he is there to guide the students, not direct them. "I really don't like giving students ideas," he explains. "I only want [them] to expand on theirs. That [factor is] a key element of [being] a mentor."

Ed Smith, president of Avnet Electronics Marketing Americas, has previously mentored younger employees and interns at the company and has also tried to develop next-generation talent as a former president of the National Electronics Distributors Association Education Foundation. Smith advises mentors to listen more than they talk when working with their students. He also reminds mentors to be cautious of time commitments when entering a mentoring relationship. Recognition that the student's time is as valuable as the mentor's time is significant. "Don't do it unless you have the right amount of time," says Smith. "If you don't have the right amount of time, it really frustrates [the mentees]. They don't feel important."

Respecting the importance of the mentees, not only about their available time but also about the value of their ideas, goes a long way and is key to a rewarding experience for both parties. "A lot of these students tend to take us under their wing, as well," says Stewart Christie, product-marketing engineer in the intelligent-systems group at Intel. Christie works with interns at Intel; is engaged in student robotics and STEM activities at local schools; and often acts as a judge and a mentor in student competitions, including this spring's Cornell Cup, a college-level embeddeddesign competition. Intel and Tektronix sponsor this competition, which gives teams the opportunity to win as much as \$10,000 (references 3 and 4). "It's great to have the fresh perspective and a much younger outlook than some of

us here have [at the office]. It's a mutual respect," Christie says.

"We who have been in the work force for a long [time] don't appreciate that what took us awhile to learn these young kids seem to have in their genes," says Pranav Mehta, senior principal engineer and chief technology officer for the intelligent-systems group at Intel. "It is amazing how advanced they are. If you just point them in the right direction, the kind of results that they can produce is mind-boggling. Many of my years-old assumptions shatter in seconds. Knowledge of society and the collective conscience has advanced to a point where these kids just see things that some of us cannot."

That excellence has encouraged Intel, as well as Avnet and TI, to hire many of its mentored interns. The companies often bring in young talent through internships or cooperative arrangements and then place them into rotational programs, allowing them to test-drive several design and business units. "As you increase the number of students coming in from college campuses, it's more important to have very robust development programs," says TI's Lyle, who notes that even TI's current chief executive officer, Rich Templeton, started at TI on a rotational basis. "We want to expose them to as many aspects of TI as possible so that they feel like they are getting a good start at the company."

The companies rarely work a continued mentoring responsibility into job descriptions, but, as Lyle says, "Part of being a leader is leading people. Part of leading a group is either directly providing that mentorship or ensuring that individuals in the organization, especially your high-potential talent, have the proper mentorship. It's not necessarily written down in everyone's job description, but it is understood

#### JOIN THE CONVERSATION

EDN recently asked its online readers what they could do each day to help inspire more interest in STEM. Share your answer and review other responses from your peers at http://bit.ly/zC6wYA.

that [mentoring] is an important part of leadership."

#### **GETTING ON THE STEM PATH**

Chris Gammell, a 28-year-old analog engineer, didn't wander into STEM until a high-school physics class sparked an interest. "My high-school physics teacher was really engaging," he says. "That set it off. I was always a science geek, but I had never done electronics before that. That's a big problem.

"My first digging into circuits was a co-op, and I just kind of hacked along," Gammell explains. "I'm a big proponent of co-ops. That's where I really learned how to solder. Someone finally sat me down and said, 'You're doing this wrong; let's show you how to do this.' There are a lot of engineers like that. As long as you actually want to listen and learn and you aren't egotistical about it, mentors are around and are gold."

Mentoring college students, interns, and entry-level employees helps cement STEM interest and give rise to young careers—a necessary effort because 45% of students who receive engineering degrees are not practicing engineers 10 years later, according to the ASEE (American Society of Engineering Education). But tapping interest at a younger age is important, as well. "[Kindergarten to Grade 12] is where it all starts," says Susan Donohue, general co-chairwoman of the IEEE Integrated STEM Education Conference, program chairwoman elect of the ASEE K-12 program, and lecturer at the University of Virginia School of Engineering and Applied Science. "If you [shortchange] them at the K-12 level, it's going to be so hard for them to catch up, and we can't afford to lose anybody."

Donohue has for several years been presenting engineering-teaching-kit workshops through the ASEE and Frontiers in Education. These kits include such tools as lesson plans, objectives, worksheets, bills of materials, and project materials, when possible. The self-contained kits enable teachers to open them and immediately bring more STEM into the classroom.

National Instruments has also taken steps to bring more STEM directly into the K-12 classroom. "We've had data come in that suggests that, if we don't have [children] interested before seventh and eighth grade, the likelihood

## Modularity meets diversity –

# R&S®VTE, the new universal test platform for MHL interface measurements

As unique as your application as compact, scalable and automated is our R&S®VTE – the new Video Tester from Rohde & Schwarz. It is ideal for measuring interface conformity of protocol and media content – both in R&D and quality assurance.

Take your AV testing to the very next level:

- Source, sink and dongle testing of the MHL 1.2 interface

- Difference picture analysis in realtime for testing transmission of video over LTE

- Future-ready modular concept accommodating up to three measurement modules

- Localizable touchscreen user interface

- Integrated test automation with protocol generation

A measurable edge in analyzing AV signals. Test and measurement solutions from Rohde & Schwarz.

The "Spectacular Seven" team from Oak Canyon Junior High in Lindon, UT, was the winner of the iGen fall 2011 LED Challenge.

[that they will go] into an engineering career is less," says Amanda Webster, community-relations manager at NI. For that reason, NI partners with Lego Group for educational robots and includes work with the FLL (FIRST Lego League) among its STEM and mentoring activities. FLL is an alliance between FIRST and the Lego Group that uses robotics to ramp up excitement about STEM at an earlier age than the FIRST Robotics Competition or FIRST Tech Challenge.

"I don't think that Dr T, our founder, thought that, years down the road, this high-tech company would be partnering with this toy company. But, with Lego being a top brand ..., it has been a huge opportunity for us to get into the K-12 space," says Webster. "[Lego] lends credibility when you are standing in front of a 7-year-old trying to get him or her interested in math and science concepts that, unfortunately, even young children are showing a disinterest in."